SERDES 技术

SERDES 技术

SerDes技术是用于高速串行链路中的技术,是一种主流的时分多路复用(TDM)、点对点(P2P)串行通信技术。Ser代表串化器(Serializer),Des代表解串器(Deserializer),主要功能是将低速并行信号转化为高速低压拆分信号(LVDS)并通过串行里链路发送,同时能够接收串行输入LVDS信号并正确转化为低速并行信号,简单来讲就是并串与串并的转化。目前SERDES的应用,主要有Chip2Chip,Board2Board,Box2Box等形式,在大型数据中心,通信骨干网络,消费电子场景下有广泛应用。

SERDES 背景知识

-

差分传输技术LVDS:

区别于传统一根信号线一根地线的做法,差分传输在两根线上都传输信号,两个信号振幅相同,相位相反,两根线上的传输信号即为差分信号。信号接收端通过比较两个电压的差值来判断发送端发送信息的逻辑状态。LVDS是一种低摆幅的差分信号技术,高速且低功耗,抗干扰能力强,外界的共模噪声可以被完全抵消。

-

串/并口技术与芯片同步技术:

数据传输最开始是低速串行接口(Serial Interface)简称串口,为了提高数据总带宽,人们首先想到的是增加数据的位宽,提升传输速率,故而引入了并行接口(Parallel Interface)简称并口。但随着并口发展,并口限制也逐渐凸显:

- 芯片IO口数量紧张;

- 并口数据率提升过程中引入的串扰(Cross-Talk)和同步切换噪声(SSN=,L指芯片封装电感,N指数据位宽,指电流变化率)使得数据同步越来越困难。

因此高速串口技术重新得到发展。

串并口的演进是交替发展的。串口典型代表是通用串行总线(Universal Serial Bus,USB),并口有DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory,DDRx)。SerDes虽然是串口技术,也可以多通道并行使用,比如PCIe协议的x4、x8、x16模式,但需要考虑多通道对齐的问题。高速串口未来的发展趋势是提升单通道速度和多通道并行相结合。 -

芯片同步技术:

大部分数字电路都采用同步电路模式,即系统中有一个统一的时钟对信号进行采样。芯片与芯片间的同步接口通信有三种时序模型:1. 系统同步;2. 源同步;3. 自同步。系统同步指的是外接时钟信号对信源和信宿进行同步;源同步指的是信源发送数据至FPGA后,FPGA生成一个伴随时钟信号提供给信宿进行同步;自同步指的是信源芯片自身提供时钟信号同步,自同步接口的三个主要模块分别是并串转换、串并转换、时钟数据恢复,即SerDes技术的主要实现方式。

速率较低时系统同步即可满足要求,但随着速率提升,严格的时序要求使用源同步或自同步。

-

8B/10B编码技术:

该技术主要解决的问题是实现直流均衡。信号频率越高,电容阻抗越低,但当数据位流中出现多个连续的1或0时,该时间段信号可认为是直流,电容损耗变大,导致信宿端接收到的信号幅度降低,无法识别0还是1。而且信宿端接收到连续的0或1时,没有充分定时信息,对解码带来困难。8B/10B编码技术通过将原8位信号拆解成3位和5位,并通过3B/4B、5B/6B编码映射成一个4位和一个6位信号,再根据编码表平衡实际传输信号中的0和1的数量。该编码通过引入极性偏差(Running Disparity,RD)来判断编码后0和1谁多,通过RD来决定4位信号与6位信号该如何组合,共同形成一个实际传输的10位信号,从而缓解长0或长1信号的目的。

-

锁相环(PLL):

由鉴相器(Phase Discriminator,PD),环路滤波器(Loop Filter,LF),和压控振荡器(Voltage-Controlled Oscillator,VCO)构成。同时内部还有一个反馈路径(Feedback Path)构成一个环电路,故而称为锁相环。锁相环最早在20世纪30年代被提出,广泛用于电子系统中,提供稳定信号频率、相位和时序的功能。在数字电路和通信领域,PLL可以用来提取、跟踪、复原和生成特定频率的信号,以实现数据同步、时钟分配和频率调整(8x、20x、40x模式多倍频)等功能。

SERDES 介绍

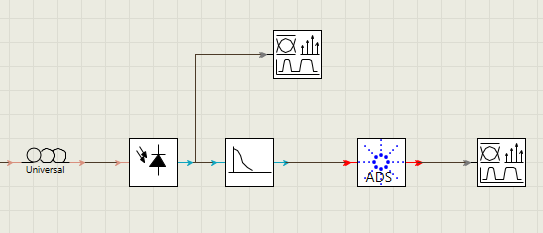

一个完整的8B/10B SERDES模块如下,其中Serializer由8B/10B编码器、PRBS码生成器、串并转换电路、差分信号发送器、PLL等模块构成;Deserializer则由差分信号接收器、CDR、串并转换电路和8B/10B解码器构成,整体结构如下

SERDES接口简化示意图如下

时钟速率位125 MHz的8位并行数据,经过复用器芯片时分复用到1位的数据线上,转化为1 Gbps的1位串行数据。该数据经过发送器Tx,通道Channel,再到接收器Rx处理后仍为1 Gbps,解串后恢复为初始125 MHz的8位并行数据。

-

时钟数据生成与恢复:

最高10 Gbps的数据率,内部需要至少10 GHz的时钟(Single Data Rate,SDR)或者5 GHz的时钟(Double Data Rate,DDR)。SERDES内部依靠PLL实现频率稳定,同步控制与时钟数据恢复(Clock Data Recovery,CDR),降低时间抖动jitter。CDR的功能:通过调整本地时钟的相位完成对带有信道损耗(Channel Loss)和各级模块噪声(Noise)的接收Tx串行数据的重定位,找到最佳采样时刻,使Rx本地时钟边沿与接收Tx数据中心位置对齐,实现最佳采样。

-

预加重(Pre-Emphasis)和去加重(De-Emphasis):

预加重和去加重都是在发送端对输入信号高频分量进行补偿的信号处理方式(与预均衡Tx-EQ等价)。一般的SERDES结构中,发送端有预加重模块(加重器),接收端有均衡模块。预加重是通过加大信号的上升沿和下降沿幅度来增强信号高频分量,去加重是通过保持上升沿下降沿幅度不变,降低其他地方幅度来实现信号高频分量相比低频分量增大。去加重补偿后信号摆幅比预加重更小,眼图高度低功耗小,电磁辐射小。

-

均衡器(Equalizer,EQ):

-

由于信号速率不断提高且信息传输架构需要更长的传输链路,高速信号的趋肤效应和传输导线介质损耗导致高频信号在传输过程中衰减很快,Tx发送端发送的数据由于码间干扰(Inter-Symbol Interference)导致信号在Rx接收端失真严重,眼图闭合。

-

均衡器的作用就是均衡信道的衰减,缓解码间干扰,通过高通滤波器补偿信道的低通特性,将脉冲响应信号重新塑形,把能量限制在一个单位时间间隔(1 Unit Interval,1UI)内,从而把数据正确恢复出来,让闭合的眼图睁开。均衡技术主要有三种:连续时间线性均衡(Continuous Time Linear Equalizer,CTLE),判决反馈均衡(Decision Feedback Equalizer,DFE)和前馈均衡(Feed Forward Equalizer,FFE)。

-

前馈均衡(FFE):为了缓解接收端均衡的压力,通常SERDES的发送端会使用FFE对信号进行预均衡(预加重或去加重)。FFE通过有限冲激响应滤波器实现,即将延时信号按不同权重叠加,控制权重大小调整均衡强度。FFE的实质是使用数字线性高通滤波器提高信号的高频分量,实现信道补偿。然而对于发送机而言,其输出最大摆幅受限于电源电压,因此0到1或1到0的跳转电压程度无法被无限放大,这会导致信号的实际摆幅随FFE均衡强度提高而减小。因此在实际设计中,为了保证信号实际摆幅,FFE均衡强度小于10 dB。

-

连续时间线性均衡(CTLE):本质是直接通过模拟高通滤波器拟合信道的衰减,实现信道补偿。信道的频率响应可以看作一个低通滤波器,因此将信道与高通滤波器串联就能得到一个全通滤波器。实际的模拟电路中并不存在高通滤波器,但只要保证关心的带宽内呈现高通特性即可满足均衡要求。需要注意CTLE电路是通过减小低频信号的方式补偿高低频的衰减差,因此会和放大器配合使用,其缺点是在放大高频信号的同时放大高频噪声,降低信噪比,往往伴随巨大的面积和功耗开销。

-

判决反馈均衡(DFE):本质与FFE类似,也是通过数字高频滤波器实现高频信号分量的增强,各个支路的权重决定了均衡的强度。但与FFE不同的是DFE为一种非线性均衡技术:判决后的信号为数字信号而非原输入信号经过时延得到。因此DFE可以只放大高频信号而不放大高频噪声。

为了将数据正确恢复出来,需要通过均衡器均衡信道的衰减,减小数据的码间干扰。Tx端的预均衡(Pre-Equalizer)通常用FFE结构实现预加重,Rx端采用CTLE和DFE串接的方式实现信号均衡和恢复,如下图所示

-